- ภาพรวม

- สินค้าที่แนะนำ

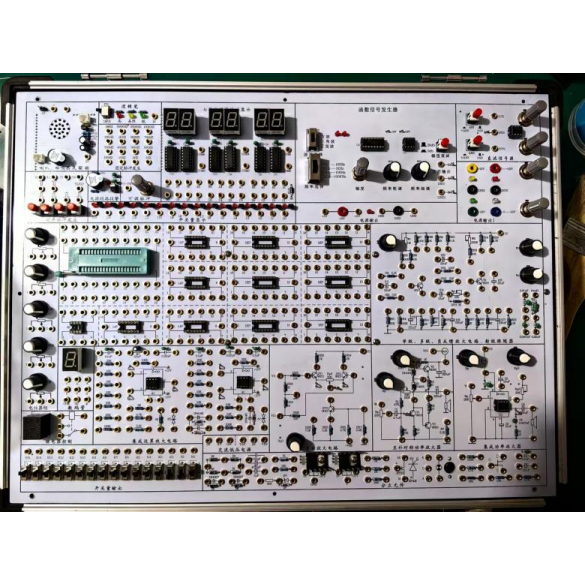

โครงสร้างวงจรเกตตรรกะ (DL, RTL, TTL และ CMOS)

ความยาวข้อมูลขาเข้า: 16 บิต

ชุดตัวต้านทานแปรค่าบนแผงวงจร—จำนวน 6 ตัว

บอร์ดทดลองวงจร (Bread Board) ขนาด 172.5 มม. × 128.5 มม.

โหมดป้อนข้อมูลขาเข้า: สวิตช์ DIP

วงจรเกตตรรกะประกอบด้วยเกต AND, เกต NAND, เกต NOT, เกต OR, เกต NOR และเกต XOR

การวัดแรงดันไฟฟ้าและกระแสไฟฟ้า (TTL, CMOS)

อินเทอร์เฟซระหว่างวงจรเกตตรรกะ (TTL, CMOS แบบแปลง)

การวัดความล่าช้าในการส่งสัญญาณ (TTL, CMOS);

ความล่าช้าในการส่งสัญญาณแบบ TTL: 20 นาโนวินาที;

ความล่าช้าในการส่งสัญญาณแบบ CMOS: 99.1 นาโนวินาที